TI E2E support forums

TI E2E™ design support forums are an engineer’s go-to source for help throughout every step of the design process. Our engineers answer your technical questions and share their knowledge to help you quickly solve your design issues.

Delta-sigma ADC basics: Understanding the delta-sigma …

2015年1月21日 · The delta-sigma (ΔΣ) analog-to-digital converter (ADC) is a mysterious construct to many engineers, shrouded in mathematical descriptions and defying clear explanations. This complexity can deter circuit designers from using this ADC topology and taking advantage of its many benefits. These converters are used in a wide variety of applications, including weigh …

disclaimer fairchild semiconductor reserves the right to make changes without further notice to any products herein to improve reliability, function, or design.

Texas Instruments 3 SLUP263 3-3 Topic 3 A. Configuration Fig. 3a shows a typical topology of an LLC resonant half-bridge converter. This circuit is very

The Instrumentation Amplifier Handbook Including Applications Neil P. Albaugh Burr- Brown Corporation Tucson, Arizona DRAFT COPY

It’s in the math: how to convert an ADC code to a voltage (part 1)

2016年4月1日 · Many newcomers to analog-to-digital converters (ADCs) wonder how to convert their ADC code to a voltage. Or perhaps their question is specific to the application, such as how to convert the ADC code back to a physical quantity like current, temperature, weight or pressure.

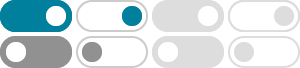

Op Amp Voltage Ranges—input and output, clearing some …

2012年5月8日 · This is really true that some op amps claim only a rail-to-rail output, lacking the input characteristics shown in figure 3. Rail-to-rail op tree chipper amps are very commonly used on single 5V supplies and lower because they maximize …

Signal 1 Power Plane GND Plane Signal 2 www.ti.com USB PHY Layout Guide Consider the recommendations listed below to achieve proper ESD/EMI performance: • Use a 0.01 μF cap on each cable power VBUS line to chassis GND close to the USB connector pin.

C28xx: Error connecting to the target: (Error -1135 @ 0x0)

Hi Gautam, Thanks for your reply, I double checked the both SW2 and SW3, they are all switched to on position. As said in the above document, LD1 is a power indicator that has to be turn on when the control card is powered.

2-1 Design And Application Guide for High Speed MOSFET Gate Drive Circuits By Laszlo Balogh ABSTRACT The main purpose of this paper is to demonstrate a systematic approach to design high performance